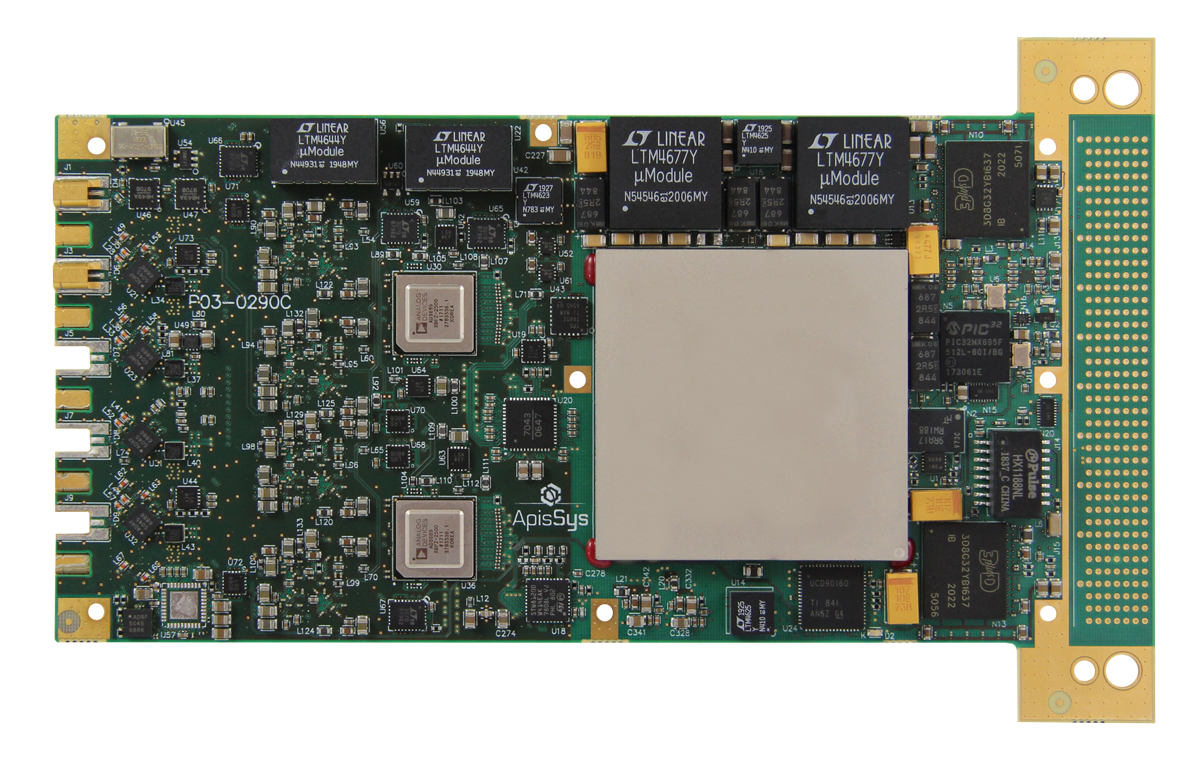

AV150

The AV150 is a component of apissys’ line of High-Speed data conversion and signal processing solutions, which adhere to the VITA 47, VPX standard.

Fully compliant with the OpenVPX standard, the AV150 supports a variety of communication protocols, including PCIe, Gigabit Ethernet and Aurora, as well as a large number of user-defined I/O.

The AV150 combines four 14-bit 3 Gsps ADCs and four 16-bit 6/12 Gsps DAC with ultra-high processing power delivered by an AMD Virtex® Ultrascale+™ FPGA (VU7P/VU9P/VU13P).

AMD Virtex® UltraScale+™ FPGAs provide the highest performance and integration capabilities in a 14 nm/16 nm FinFET node. In addition, they offer the highest transceiver bandwidth, highest DSP count, and highest on-chip and in-package memory available in the UltraScale™ architecture. Virtex® UltraScale+™ FPGAs also provide numerous power options that deliver the optimum balance between the required system performance and the smallest power envelope.

Target markets of this AV150 VPX board include Phased-Array Radar Transmitter / Receiver, Electronic Warfare ESM /ECM, MIMO and Wideband Communication.